在當(dāng)今萬(wàn)物互聯(lián)、邊緣計(jì)算蓬勃發(fā)展的時(shí)代,嵌入式系統(tǒng)作為連接物理世界與數(shù)字世界的核心樞紐,其開(kāi)發(fā)效率與系統(tǒng)性能至關(guān)重要。AMD憑借其強(qiáng)大的異構(gòu)計(jì)算能力與深厚的技術(shù)積淀,構(gòu)建了一套成熟、高效的嵌入式開(kāi)發(fā)框架。這一框架并非單一工具,而是一個(gè)由三大基石構(gòu)成的完整生態(tài)系統(tǒng),它們共同作用,旨在降低開(kāi)發(fā)門(mén)檻,加速產(chǎn)品上市,并充分釋放AMD嵌入式硬件(如Zynq UltraScale+ MPSoC、Versal ACAP等)的澎湃性能。深入理解這三大基石,對(duì)于嵌入式軟件開(kāi)發(fā)工程師而言,是駕馭AMD平臺(tái)、實(shí)現(xiàn)創(chuàng)新應(yīng)用的關(guān)鍵。

基石一:Vitis? 統(tǒng)一軟件平臺(tái)

Vitis? 平臺(tái)是AMD嵌入式開(kāi)發(fā)框架的核心與靈魂。它打破了傳統(tǒng)FPGA開(kāi)發(fā)與處理器軟件開(kāi)發(fā)之間的壁壘,提供了一個(gè)統(tǒng)一的開(kāi)發(fā)環(huán)境,支持從邊緣到云的全方位應(yīng)用開(kāi)發(fā)。對(duì)于軟件開(kāi)發(fā)人員,Vitis的核心價(jià)值在于其“硬件自適應(yīng)”的編程理念。

- 抽象化硬件復(fù)雜性:通過(guò)Vitis,開(kāi)發(fā)者可以使用C、C++或OpenCL等高級(jí)語(yǔ)言進(jìn)行開(kāi)發(fā),而無(wú)需深入掌握硬件描述語(yǔ)言(如Verilog/VHDL)。Vitis編譯器與鏈接器會(huì)自動(dòng)將代碼中的計(jì)算密集型部分映射到可編程邏輯(PL)端,形成硬件加速內(nèi)核(Kernel),而控制流和順序代碼則運(yùn)行在處理器系統(tǒng)(PS)端。這種軟硬件協(xié)同設(shè)計(jì)的抽象,極大地提升了開(kāi)發(fā)效率。

- 豐富的加速庫(kù):Vitis提供了Vitis加速庫(kù)(Vitis Libraries),包含針對(duì)視頻編解碼、圖像處理、數(shù)據(jù)分析、金融科技等領(lǐng)域的預(yù)優(yōu)化、開(kāi)源的硬件加速函數(shù)。開(kāi)發(fā)者可以像調(diào)用軟件庫(kù)一樣使用它們,快速構(gòu)建高性能應(yīng)用,避免了從零開(kāi)始設(shè)計(jì)硬件加速器的巨大工作量。

- 目標(biāo)平臺(tái)無(wú)關(guān)性:Vitis支持“一次編寫(xiě),多處部署”。開(kāi)發(fā)者可以在x86服務(wù)器上進(jìn)行功能驗(yàn)證和性能剖析,然后無(wú)縫地將應(yīng)用部署到AMD的嵌入式板卡或云端FPGA實(shí)例上,極大地簡(jiǎn)化了開(kāi)發(fā)與測(cè)試流程。

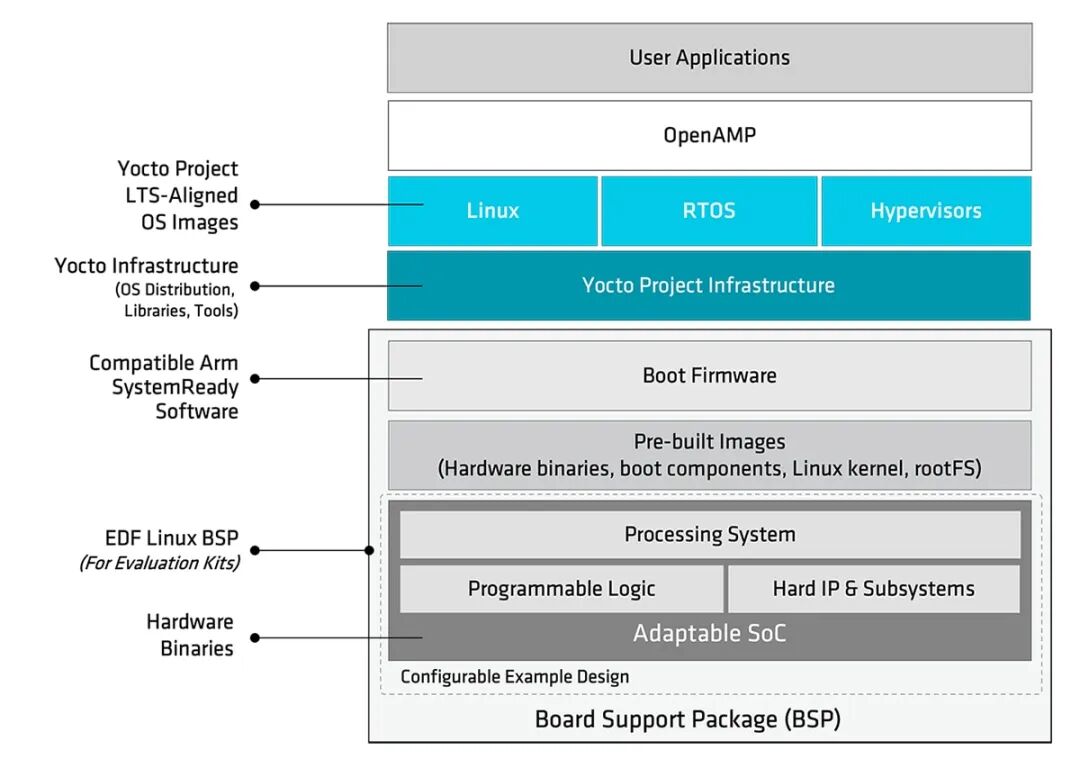

基石二:PetaLinux? 工具與系統(tǒng)軟件

對(duì)于運(yùn)行復(fù)雜操作系統(tǒng)(尤其是Linux)的嵌入式應(yīng)用,系統(tǒng)軟件的構(gòu)建、定制與優(yōu)化是另一大挑戰(zhàn)。PetaLinux? 工具集正是為此而生,它是基于Yocto項(xiàng)目的高度定制化工具,專(zhuān)門(mén)用于為AMD SoC和ACAP器件構(gòu)建、調(diào)試和部署嵌入式Linux系統(tǒng)。

- 自動(dòng)化系統(tǒng)鏡像生成:PetaLinux可以根據(jù)硬件設(shè)計(jì)(由Vivado? Design Suite導(dǎo)出)自動(dòng)配置Linux內(nèi)核、設(shè)備樹(shù)(Device Tree)、根文件系統(tǒng)以及引導(dǎo)加載程序(Bootloader)。開(kāi)發(fā)者只需通過(guò)簡(jiǎn)單的命令和配置文件,即可生成一個(gè)完整且與硬件精確匹配的啟動(dòng)鏡像,確保了軟硬件的一致性與可靠性。

- 深度定制與集成:它允許開(kāi)發(fā)者輕松添加自定義內(nèi)核模塊、用戶(hù)空間應(yīng)用程序、第三方庫(kù),并對(duì)內(nèi)核進(jìn)行深度裁剪,以生成滿(mǎn)足特定應(yīng)用需求(如尺寸、啟動(dòng)時(shí)間、實(shí)時(shí)性)的精簡(jiǎn)系統(tǒng)。這對(duì)于資源受限的嵌入式環(huán)境尤為重要。

- 簡(jiǎn)化驅(qū)動(dòng)開(kāi)發(fā)與調(diào)試:PetaLinux與Vitis緊密集成,能夠自動(dòng)為Vitis中創(chuàng)建的硬件加速I(mǎi)P生成Linux設(shè)備驅(qū)動(dòng)和用戶(hù)空間API(如Xilinx Runtime, XRT),使得軟件應(yīng)用可以方便地調(diào)用硬件加速功能。其內(nèi)置的調(diào)試工具也極大地方便了系統(tǒng)級(jí)問(wèn)題的定位。

基石三:Vitis? AI 開(kāi)發(fā)環(huán)境

隨著人工智能在邊緣端的廣泛部署,嵌入式設(shè)備的AI推理能力成為關(guān)鍵需求。Vitis? AI是AMD專(zhuān)為AI推理打造的開(kāi)發(fā)平臺(tái),是前兩大基石的強(qiáng)大延伸,使開(kāi)發(fā)者能夠輕松地將深度學(xué)習(xí)模型部署到AMD嵌入式設(shè)備上。

- 完整的模型部署流水線(xiàn):Vitis AI提供了一套從主流框架(如TensorFlow, PyTorch)到AMD硬件的高效路徑。它包括模型量化、編譯、優(yōu)化和部署工具鏈。開(kāi)發(fā)者可以將訓(xùn)練好的浮點(diǎn)模型,通過(guò)量化工具轉(zhuǎn)換為低比特寬(如INT8)模型,在幾乎不損失精度的情況下大幅提升能效比和吞吐量。

- 預(yù)優(yōu)化AI模型與IP庫(kù):Vitis AI Model Zoo提供了一系列針對(duì)AMD硬件深度優(yōu)化的預(yù)訓(xùn)練模型,涵蓋分類(lèi)、檢測(cè)、分割等多個(gè)領(lǐng)域,開(kāi)箱即用。其高效的AI推理引擎(DPU)作為可配置的IP,可以通過(guò)Vivado集成到硬件設(shè)計(jì)中,并通過(guò)Vitis和PetaLinux提供完整的軟件棧支持。

- 統(tǒng)一的高層次API:Vitis AI Runtime(VART)提供了一套簡(jiǎn)潔的C++/Python API,使得在嵌入式Linux或裸機(jī)環(huán)境中調(diào)用DPU進(jìn)行推理變得異常簡(jiǎn)單,軟件開(kāi)發(fā)者無(wú)需關(guān)心底層硬件細(xì)節(jié),即可實(shí)現(xiàn)高性能AI應(yīng)用。

協(xié)同工作:構(gòu)建高效開(kāi)發(fā)流

這三大基石并非孤立存在,而是環(huán)環(huán)相扣,形成一個(gè)流暢的開(kāi)發(fā)閉環(huán):

- 從硬件定義開(kāi)始:在Vivado中完成硬件平臺(tái)設(shè)計(jì)(包含處理器系統(tǒng)、外設(shè)及硬件加速I(mǎi)P),導(dǎo)出XSA文件。

- 構(gòu)建軟件系統(tǒng):使用PetaLinux,導(dǎo)入XSA文件,配置并生成包含Linux系統(tǒng)、驅(qū)動(dòng)及文件系統(tǒng)的啟動(dòng)鏡像。

- 開(kāi)發(fā)加速應(yīng)用:在Vitis中,基于同一硬件平臺(tái),利用高級(jí)語(yǔ)言開(kāi)發(fā)主機(jī)應(yīng)用程序和硬件加速內(nèi)核,并可集成Vitis AI編譯生成的AI模型。

- 集成與部署:將Vitis生成的應(yīng)用可執(zhí)行文件與PetaLinux生成的系統(tǒng)鏡像結(jié)合,最終燒錄到目標(biāo)板卡,完成部署。

###

AMD嵌入式開(kāi)發(fā)框架的這三大基石——Vitis統(tǒng)一軟件平臺(tái)、PetaLinux系統(tǒng)工具和Vitis AI開(kāi)發(fā)環(huán)境——共同構(gòu)建了一個(gè)從底層硬件到上層應(yīng)用,從傳統(tǒng)控制到AI推理的全棧式解決方案。它們通過(guò)高度的抽象、自動(dòng)化和優(yōu)化,將復(fù)雜的異構(gòu)計(jì)算硬件潛力轉(zhuǎn)化為軟件開(kāi)發(fā)者的生產(chǎn)力,使得工程師能夠更專(zhuān)注于算法創(chuàng)新與應(yīng)用實(shí)現(xiàn),而非底層硬件適配。深入掌握并靈活運(yùn)用這三大基石,是在AMD嵌入式平臺(tái)上進(jìn)行高效、高性能軟件開(kāi)發(fā)的不二法門(mén)。